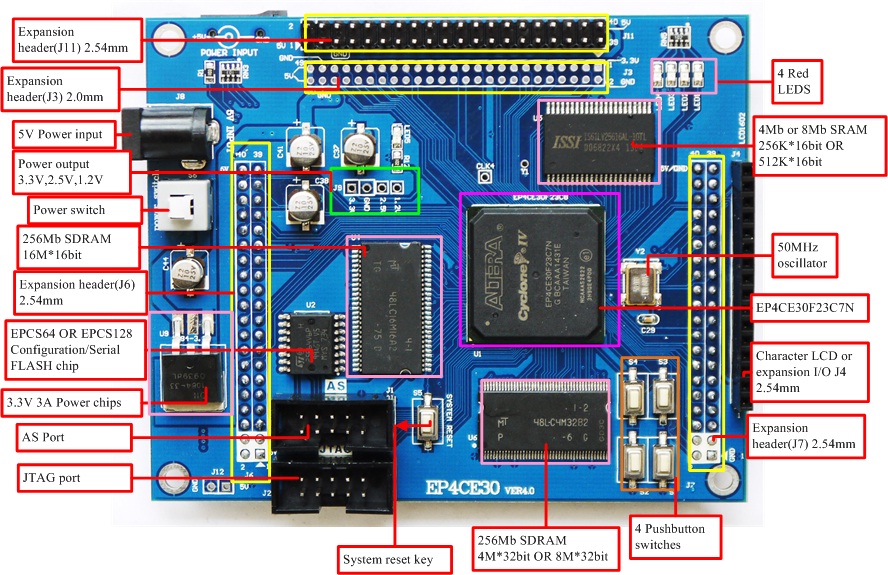

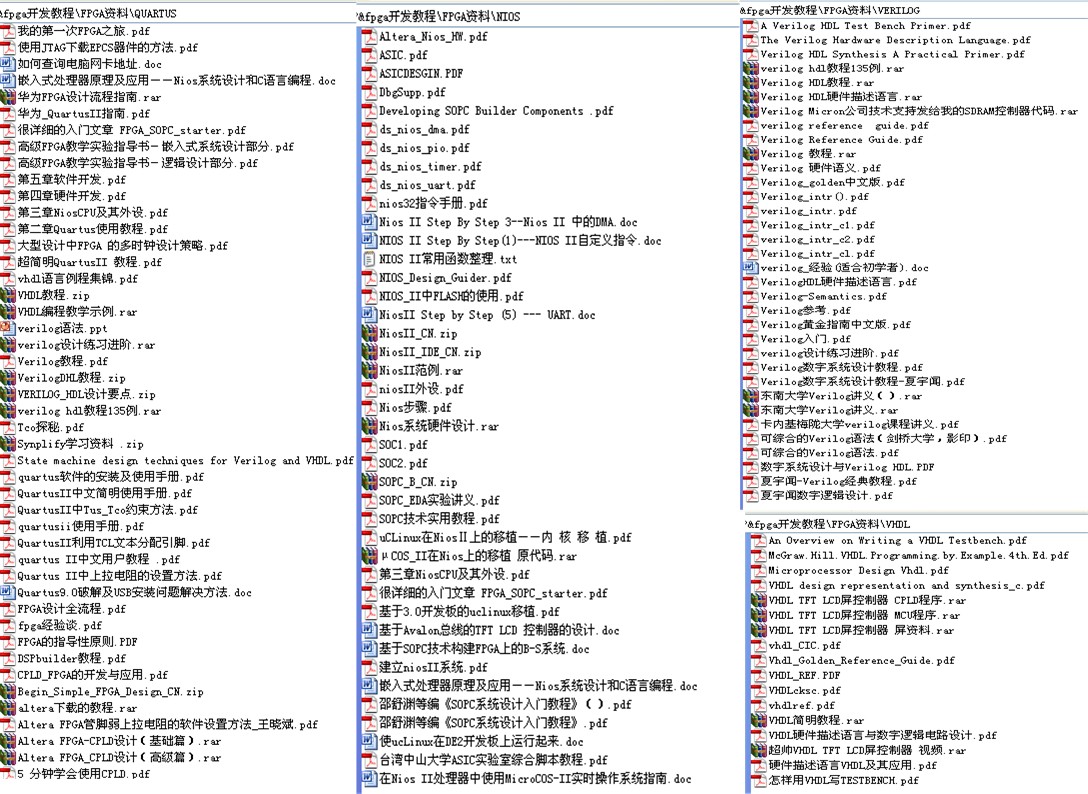

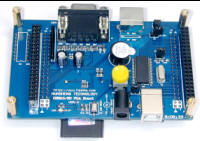

EP4CE30F23C8NетПюаОЦЌВЩгУОЙ§гХЛЏЕФ60-nmЕЭЙІКФЙЄвеЃЌCyclone IV/E FPGAЭиеЙСЫЧАвЛДњCyclone III FPGAЕФЕЭЙІКФгХЪЦЁЃ аТвЛДњЦїМўНЕЕЭСЫФкКЫЕчбЙЃЌгыЧАвЛДњВњЦЗЯрБШЃЌзмЙІКФНЕЕЭСЫ25ЃЅЁЃ

КЫаФАхАхВЩгУЪЧСљВуPCBЩшМЦЃЌВЩгУДѓШнСПЙмНХИќЖрЕФBGAЗтзАЃЌF484ЗтзАЃЌЪЙећИіКЫаФАхЕФадФмКЭЮШЖЈадгаСЫКмДѓЕФЬсЙЉЃЌВЂЭЌЪБЮЊгУЛЇЬсЙЉДѓСПЕФгааЇI/OЃЈЖРСЂI/OвЛЙВЪЧ131ИіЃЉЁЃ

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ЁЁ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

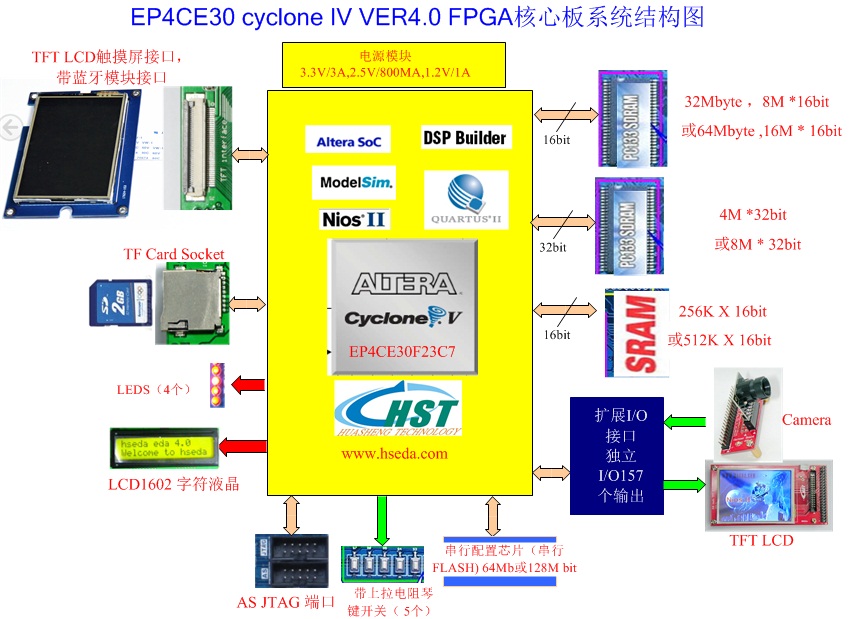

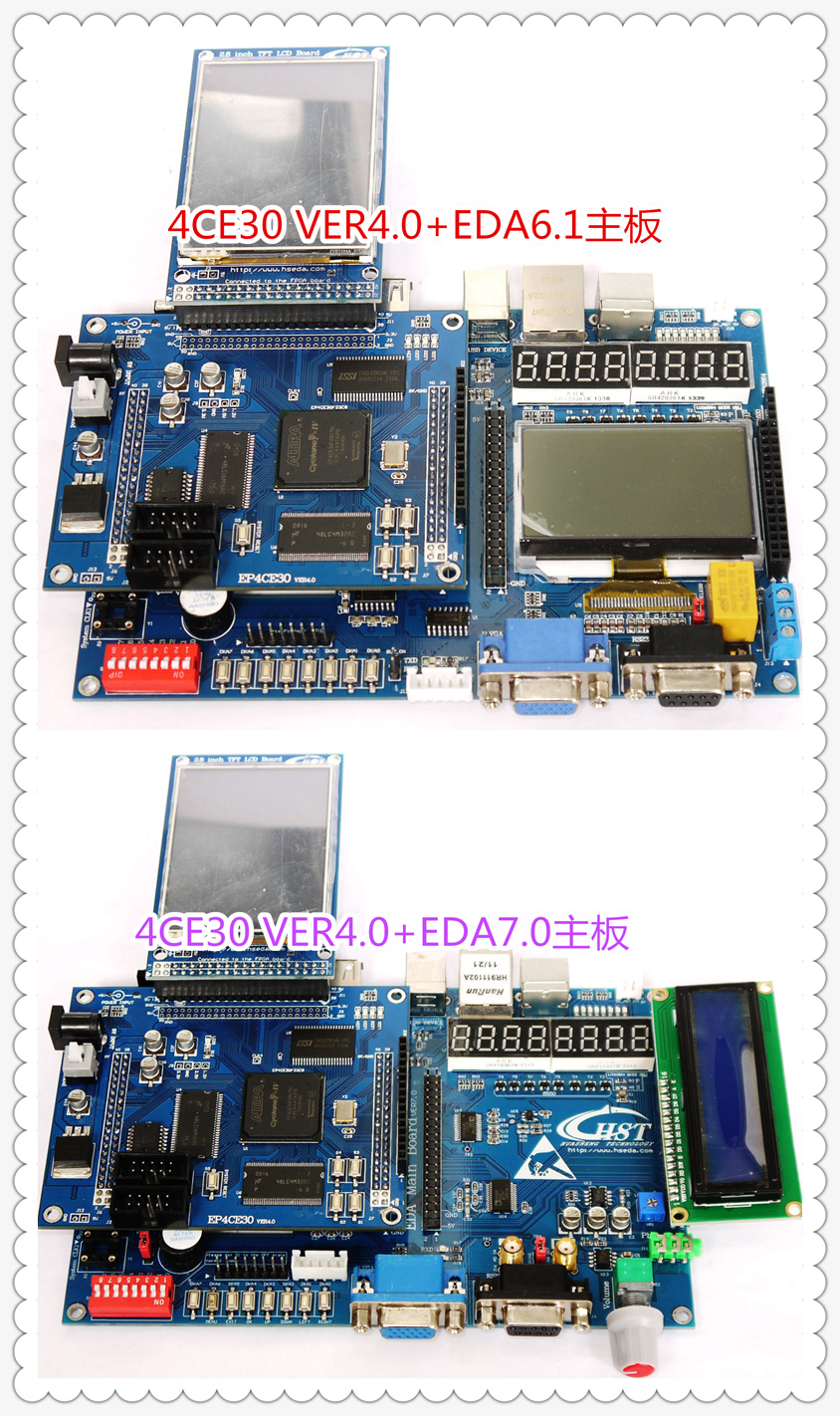

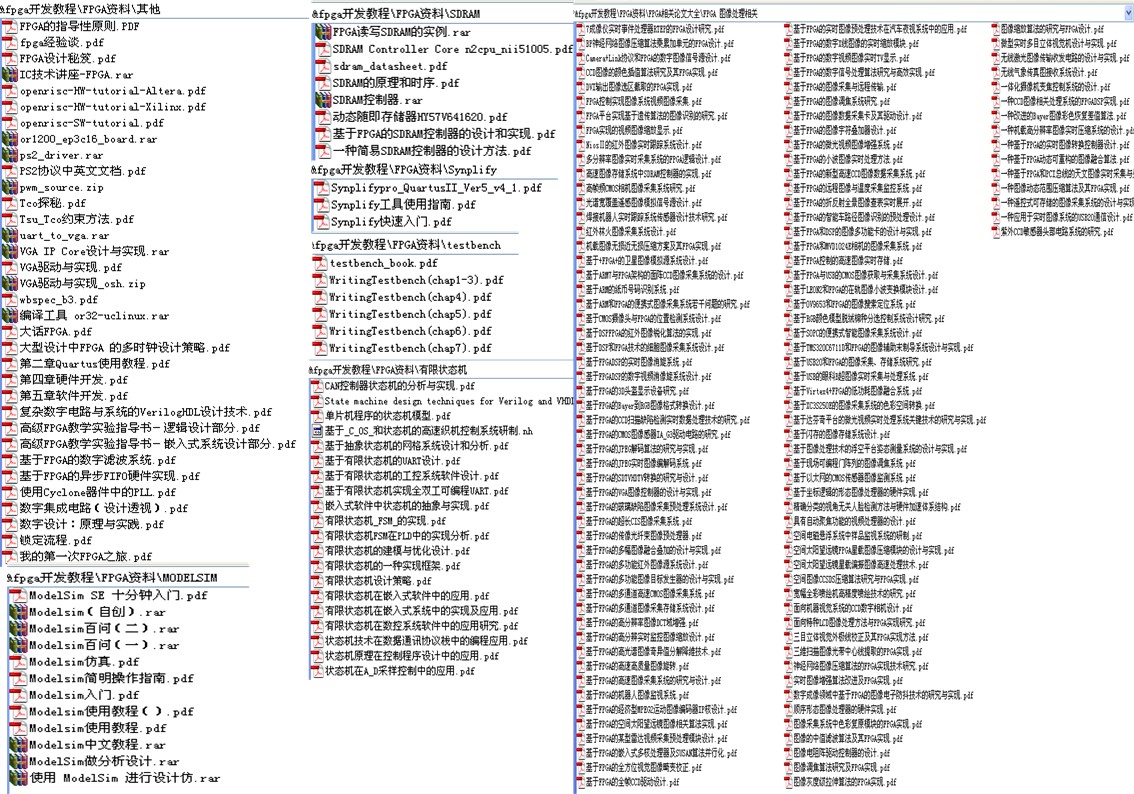

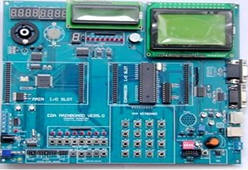

CYCLONE IV EP4CE30 VER4.0 NIOS2 SOPC 32bitИпЫйЪ§ОнВЩМЏЦЙХвЫуЗЈFPGAПЊЗЂАх вЛЁЂМђНщ гЩгкFPGAгыДцДЂЦїжБНгНјааИпЫйЪ§ОнНЛЛЛЁЃЫљвдГЩдкКмЖрИЩШХвђЫиЃЌвђДЫетвВЪЧКмЖр ПЊЗЂАхЫйЖШКмФбЬсИпЕФЙиМќдвђЁЃЫљвдЮвУЧдкЩшМЦЕФЪБКђОЁСПППНќFPGAаОЦЌЁЃетбљОЭ ДѓЯоЖШМѕЩйвђЮЊВМАхЫљдьГЩЕФИЩШХвђЫиЁЃ ЮвУЧЕФПЊЗЂАхЕФ2ИіЖРСЂЕФЕФSDRAMКЭSRAMЖМВЩгУЖРСЂЕФЪ§ОнЕижЗзмЯпНјааПижЦЁЃетбљОЭЮЊЪЙгУепЬсЙЉСЫИќМгЗНУцСщЛюЕФЩшМЦЭООЖ ЃЌ2ИіЖРСЂЕФSDRAMПЩвдЗНБуЕФзіИпЫйЕФЪ§ОнДІРэЕФЦЙХвЫуЗЈПижЦЃЌЛђвЛИіSDRAMзіNIOSЕФГЬађДцДЂЃЌСэЭтвЛИізіИпЫйЕФDMAЕФЪ§ОнДцДЂЃЌ ИпЫйЖШПЩвдЕН166M. гЩгкВМЯпКЯРэЁЃетПщПЊЗЂАхЕФNIOSФмЙЛЮШЖЈИпЫйдЫаадк100MЦЕТЪвдЩЯЁЃЪЧФњзіЯЕЭГЦРЙРЛђжБНгМцШн жегІгУВњЦЗ бЁдёЁЃ гУЛЇШчЙћОѕЕУздМКзіФПБъАхТщЗГЁЃПЩвдЙКТђЮвУЧЬсЙЉЕФЖржжРЉеЙАхЁЃЃЈБОЙЋЫОгаИїжжЪгЦЕВЩМЏЃЌЪфГіРЉеЙАхЃЉЛђЪЧЭЈЙ§J6,J7жБНгВхЕНЮвУЧЕФEDAЕзАхЩЯ(EDA4.1,EDA5.1ЃЌEDA6.1ЃЌEDA7.0ЫФжжВЛЭЌПЩбЁдёжїАх)ЛђЪЧEDAЪдбщЯфЩЯЁЃетбљОЭПЩвдГфЗжРћгУЮвУЧЕФEDAЕзАхЬсЙЉЕФЙІФмЖрбљЃЌЭъЩЦЭтЩшзЪдДЁЃетбљОЭФмЧсвзЕФЙЙГЩвЛЬзЪлМлЕЭСЎЃЌЙІФм ДѓЕФSOPCПЊЗЂ,ЦРЙРЯЕЭГЁЃ КЫаФАхЖЅВуВМОжЭМ

ЁЁ КЫаФАхЕзУцВМОжЭМ ЁЁ

ЯЕЭГНсЙЙЭМ

ЁЁ Жў.ЯЕЭГзЪдД

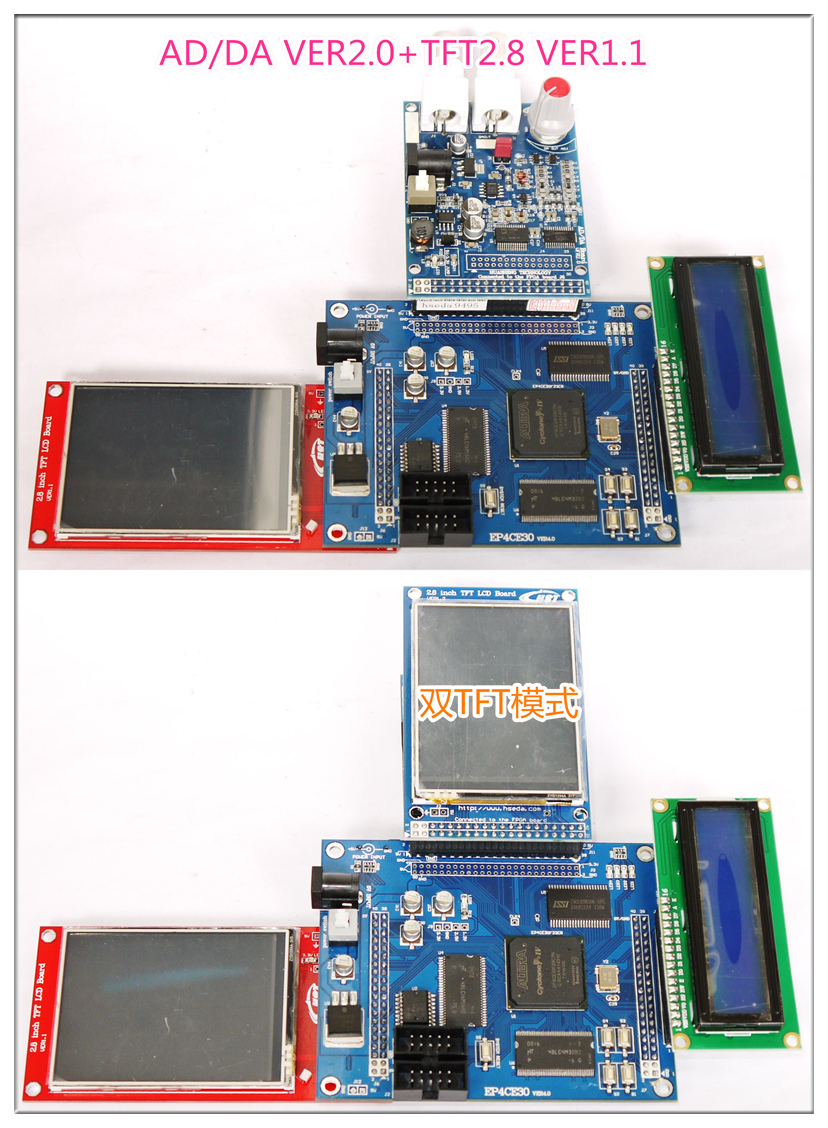

ЁЁ Ш§.КЫаФАхгыЦфЫќРЉеЙАхзщКЯ FPGAКЫаФАхгыTFT LCDЁЂAD/DA VER2.0РЉеЙАхНгПк

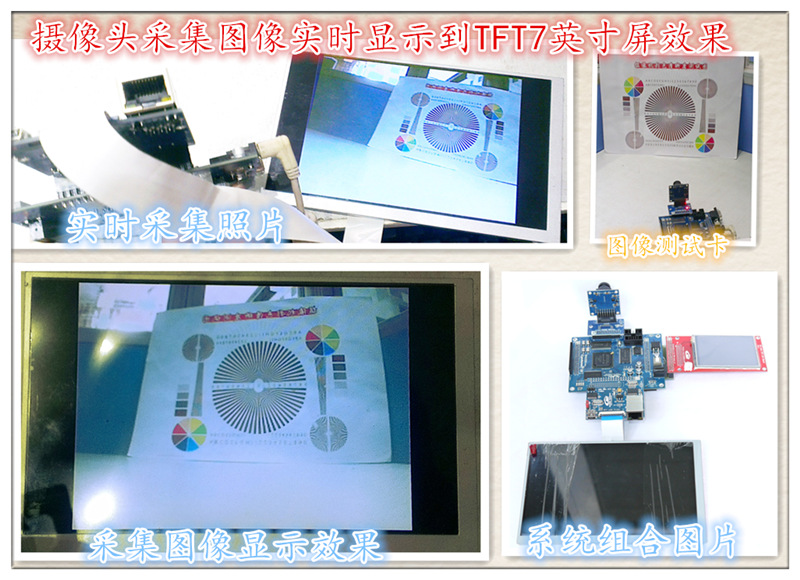

ЁЁ MT9M034+OV7670/0V7725ЫЋЩуЯёЭЗМгTFT2.8гЂДчДЅУўЦСзщКЯНсЙЙЭМ ЁЁ

ЁЁ гыEDA6.1ЛђEDA7.0жїАхзщКЯГЩEDA/SOPCПЊЗЂЪЕбщЯЕЭГ

ЁЁ ЁЁ ЫФ.ВПЗжЪЕбщаЇЙћеЙЪО

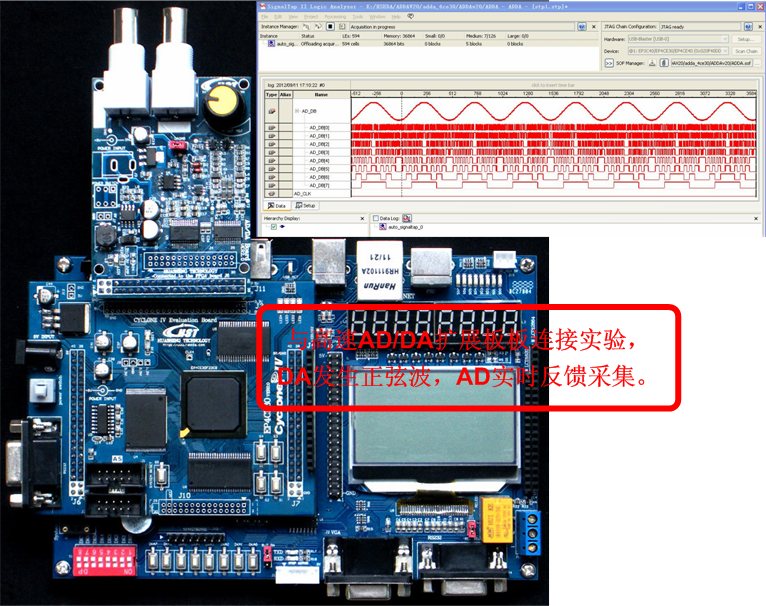

ЩуЯёЭЗВЩМЏЕН7гЂДчTFTЦСЯдЪОЪЕбщЃЈVERILOGДњТыЃЉ ЃЈДюдиNET+TFT7INCH+USBРЉеЙАхЃЉ TFT2.8гЂДчДЅУўЦСМгРЖбРФЃПщ VER4.0 ЁЁ ЁЁ ИпЫйAD/DAЪЕЪБВЩМЏЛиЗХЪЕбщЃЈDAЗЂЩњЪфГіе§ЯвВЈЃЌADЪЕЪБВЩМЏЃЉ ЪЕбщЪгЦЕЕижЗЃКhttp://v.youku.com/v_show/id_XNDU5NTc4NjAw.html ЁЁ

ЁЁ

ЁЁ

ЮхЃК

ХфЬззЪСЯ

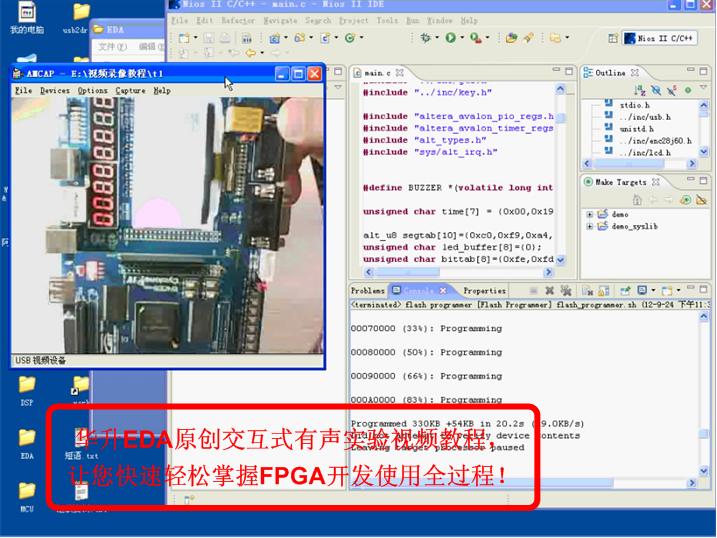

ПЊЗЂЯЕЭГХфЬзСЫ3еХDVDЙтХЬЃЌРяУцАќКЌСЫдРэЭМЃЌдДДњТыЃЌдДДНЬГЬЃЌ вдМАДѓСПЪгЦЕНЬГЬЕШЕШЁЃ ХфЬзЕФFPGAПЊЗЂШэМўЮЊЃК

Quartus II 11.0sp1 ДѓСПНЬГЬНЬГЬШУФњЧсЫЩЩЯЪж

Сљ.ЪЕбщДњТы

ЁЁ АЫ.ХфМўЧхЕЅ ЃЈБъзМХфМў)

ОХ.ПЩбЁХфМў

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||