|

||||||||||||||||||||||||||||||||||||||||||||||||||

|

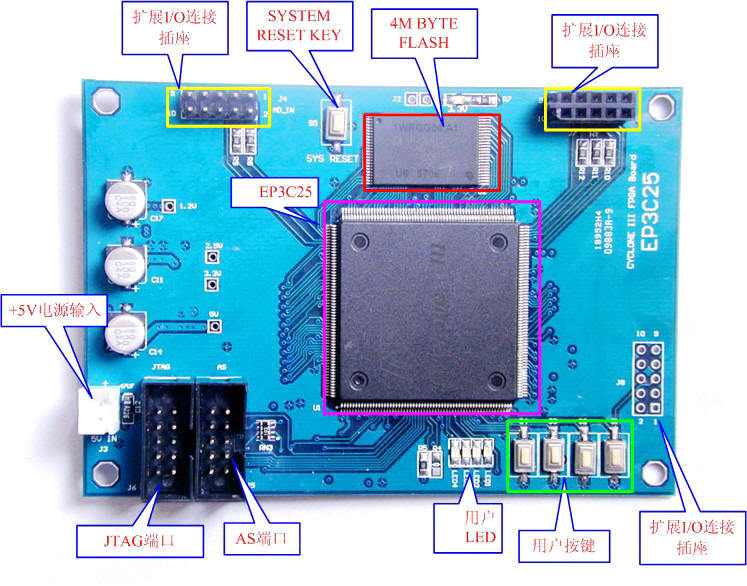

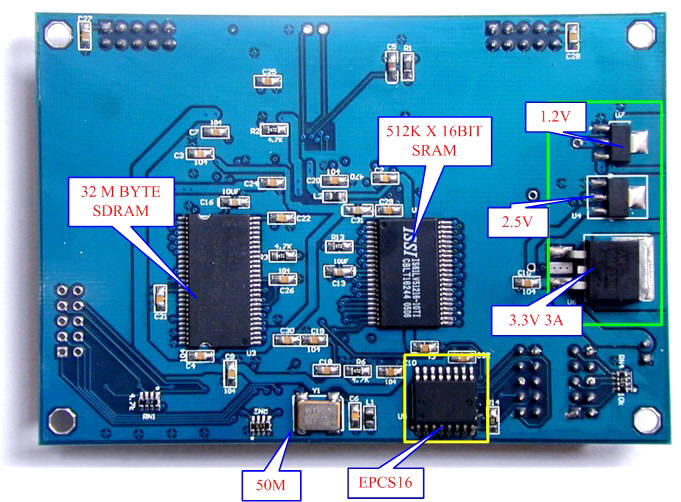

CYCLONEIII EP3C25开发板 VER1.0 标准配置售价:900(元) Logic Cells: 24624 I/O : 149 Embedded multiplier 9-bit elements: 132 Core voltage. 1.2V Memory bits: 608256 Speed Grade : 8 Plls: 4 Global clocks:20 PCB layers: 4 layers high-speed cabling design

一、简介 这块板采用4层PCB高速布线设计,SDRAM和SRAM尽量减少布线距离,所以能够运行到系统的 高频率。由于FPGA与存储器直接进行高速数据交换。所以成在很多干扰因素,因此这也是很多 开发板速度很难提高的关键原因。所以我们在设计的时候尽量靠近FPGA芯片。这样就 大限度减少因为布板所造成的干扰因素。 我们的开发板的SDRAM,FLASH,SRAM采用独立的总线.这样就为初学者提供了更加方面灵活的设计途径,并且做高速数据采集和压缩与NIOS的衔接就更加方便. 由于布线合理。这板能够稳定高速运行在100M频率以上。是您做系统评估或直接兼容 终应用产品 选择。 用户如果觉得自己做目标板麻烦。可以购买我们提供的多种扩展板。本公司已经为这块板开发了高速AD采集板,和无线通信发射板。这样就能轻易的构成一套售价低廉,功能 大的SOPC开发,评估系统。

二.系统资源

1.提供软件和试验项目: 提供全部的设计资料,包括原理图和部分扩展板的PCB,测试代码和一些IP的源码。

如:SDRAM测试程序及其源代码,系统资源分配程序(初始化程序)。LCD显示,VGA显示,数码管扫描显示,AD转换

等测试程序。PS/2键盘鼠标。QuartusII 8.1,NIOS II IDE8.1集成开发环境,niosii linux,NIOS开发教程。等等。。。。

三。相关配件

五.用户可选扩展板

|

||||||||||||||||||||||||||||||||||||||||||||||||||